什么是模块化设计

- 自下而上方法对设计进行逐次划分的过程是从基本单元出发的,设计树最末枝上的单元是已经设计好的基本单元,或者其他项目开发好的单元或者IP。该方法先对底层的功能块进行分析,然后使用这些模块来搭建规模更大的功能块,如此继续直至顶层模块。

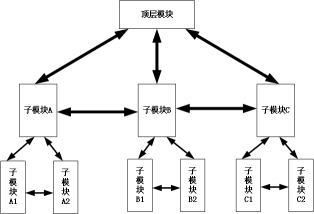

- 自上而下的设计是从系统级开始,把系统分为基本单元,然后再把每个单元划分为下一层次的基本单元,继续划分知道满足设计要求为止。该方法先定义顶层功能块,进而分析需要哪些构成顶层模块的必要子模块;然后进一步对各个子模块进行分解。

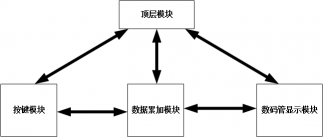

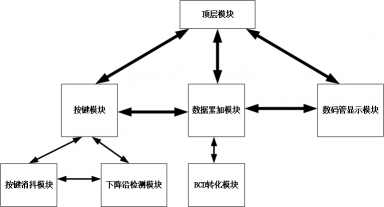

一个模块化设计实例

模块划分的方法

1、子模块功能相对独立,模块内部联系尽量紧密,而模块间的连接尽量简单。子模块的合理划分非常重要,应该综合考虑子模块的功能、结构、时序、复杂度等多方面的因素。

2、层次不要太深,一般为3~5层即可。在综合时综合工具为了获得更好的综合效果,会默认将RTL代码的层次打平(Flatten)。为了在综合后仿真和实现后仿真中较方便地找出一些中间信号,比如子模块之间的接口信号等,可 以在综合工具中设置保留结构层次,以便于查找和观察仿真信号。

3、顶层模块最好只包含对所有子模块的组织和调用,而不要完成复杂的逻辑功能。比如只写输入/输出管脚声明、模块的调用与实例化、全局时钟资源、全局置位/复位、三态Buffer和一些简单的组合逻辑。

4、子模块之间也可以有接口,但是最好不要建立子模块间跨层次的接口。例如上图中模块 A1到模块 B1之间不要直接连接,两者需要交换的信号可以通过模块 A、模块 B的接口传递。这样可以增加设计的可读性和可维护性。

1、对每个同步时序设计的子模块的输出使用寄存器。这种模块划分符合时序约束的习惯,便于利用约束属性进行时序约束,可以达到更好的时序优化效果,

2、将相关的逻辑或者可以复用的逻辑划分在同一模块内。这样可以在最大程度上复用资源,减少设计所消耗的面积。同时更利于综合工具优化某个具体功能的时序关键路径。

3、将不同优化目标的模块分开。目前很多综合与实现工具都支持物理区域位置约束,以模块为单元进行物理区域约束,就可以让综合工具仅需考虑单一的优化目标,从而使优化时序或面积就更有效。

4、可以将时序约束较松的逻辑归到同一模块。有些逻辑的时序非常宽松,不需要较高的时序约束。将这些模块归类,并指定宽松约束,则可以让综合器尽量节省面积资源和优化布局布线。

5、将存储逻辑(RAM、ROM、和 FIFO等)独立划分成模块。这样做的好处是便于利用综合约束属性显化指定这些存储单元的结构和所使用的资源类型,也便于综合器合理推断出这些逻辑所使用的固定硬件资源。

总结

- 代码具有更好的可读性,更容易理解设计的功能和数据之间的流动,更容易debug

- 代码具有更好的可复用性,能减少多次设计之间的重复工作,避免重复造轮子,提高工作效率

- 不同模块的时钟域相对独立,使跨时钟域设计之间的边界更清晰

评论(0)

您还未登录,请登录后发表或查看评论