日常·唠嗑

接上篇文章,Lattice:1、MachXO系列CPLD器件专业名词(缩略语及器件介绍),这篇文章讲一下XO系列CPLD的配置模式。

一、配置模式

1、标准协议:

所有MachXO3L/LF设备都具有通过IEEE 1149.1兼容的测试访问端口(TAP)(可以理解为JTAG) 访问的边界扫描单元。这允许通过可以访问所有关键逻辑节点的串行扫描路径对安装设备的电路板进行功能测试。内部寄存器在内部链接,允许将测试数据移入并直接加载到测试节点上,或者捕获测试数据并移出以进行验证。测试访问端口由专用的I/O组成:TDI、TDO、TCK和TMS。测试访问端口与Vccio Bank 0共享电源,可以使用LVCMOS3.3、2.5、1.8、1.5和1.2标准工作。有关边界扫描测试的更多细节,请参见使用Lattice syl /O能力的边界扫描可测试性(AN8066)和使用TransFR技术在配置过程中减少系统中断。

2、设备配置:

所有MachXO3L/LF设备都包含两个端口,可用于设备配置。测试访问端口(TAP),它支持位宽配置和sysCONFIG端口,它支持通过IPC或SPI进行串行配置。TAP既支持IEEE Standard 1149.1 Boundary Scan规范,也支持IEEE Standard 1532 In-System Configuration规范。有多种配置MachXO3L/LF设备的方法:

• Internal Flash Download

• JTAG

• Standard Serial Peripheral Interface (Master SPI mode) – interface to boot PROM memory

• System microprocessor to drive a serial slave SPI port (SSPI mode)

• Standard I2C Interface to system microprocessor

上电之后,配置SRAM就可以使用所选的sysCONFIG端口进行配置了。一旦选择了配置端口,它将在整个配置周期中保持活动状态。通过通过TAP端口发送适当的命令,可以在上电后的任何时间激活IEEE 1149.1端口。设备可以选择在进入用户模式后运行CRC检查。这将确保设备被正确配置。

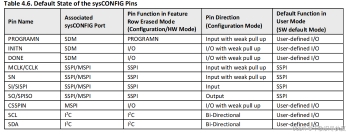

sysCONFIG端口有10个双功能引脚,如果不需要配置,可以用作通用I/O。Lattice设计软件使用专有的压缩技术来压缩位流,以用于MachXO3L/ LF设备。使用这种技术可以使Lattice提供成本更低的解决方案。在这种不太可能发生的情况下,该技术无法压缩位流以适应片上NVCM/Flash的数量,有各种各样的技术可以用于允许位流适应片上NVCM/Flash。

上表列出了共享sysCONFIG引脚的默认状态。正如你所看到的,一个HW默认模式特性行设备启用了JTAG, SPI Slave和IPC端口。进入用户模式后,MachXO3L、SSPI的默认状态和IC sysCONFIG引脚成为通用I/O。这意味着在使用默认的sysCONFIG端口设置时,您将失去使用PC编程MachXO3L的能力。要在用户模式下保留I2C sysCONFIG引脚,请确保使用Diamond电子表格视图编辑器启用它们。除非另有说明,sysCONFIG引脚由VCCIO0电压供电。在提供附加到Bank 0的其他逻辑时,一定要考虑到这一点。

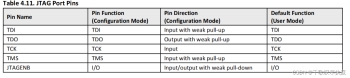

测试访问端口(TAP)有5个双用途引脚(TDI, TDO, TMS, TCK和JTAGENB)。这些引脚是双功能引脚——TDI, TDO, TMS和TCK,如果需要,可以用作通用I/O。详细信息请参见《MachXO3编程与配置使用指南(FPGA-TN-02055)》。

MachXO3LF支持基于密码的安全访问功能,也称为Flash保护键。可选地,MachXO3L设备可以与自定义规格(c-spec)一起订购以支持该功能。Flash保护键功能提供了一种方法来控制对设备的配置和编程模式的访问。当启用时,配置和编程编辑模式操作(包括写、验证和擦除操作)只有在与设备所期望的Flash保护密钥相匹配时才被允许。如果没有有效的Flash保护密钥,用户只能执行基本的非配置操作,如读取设备ID。详细信息请参见《MachXO3设备使用密码安全(FPGA-TN-02072)》。

二、配置管脚

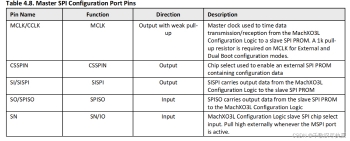

主SPI配置管脚:

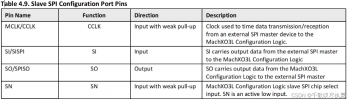

从SPI配置管脚:

JTAG配置管脚:

评论(0)

您还未登录,请登录后发表或查看评论