FPGA-结合协议时序实现UART收发器(六):仿真模块SIM_uart_drive_TB

仿真模块SIM_uart_drive_TB,仿真实现。

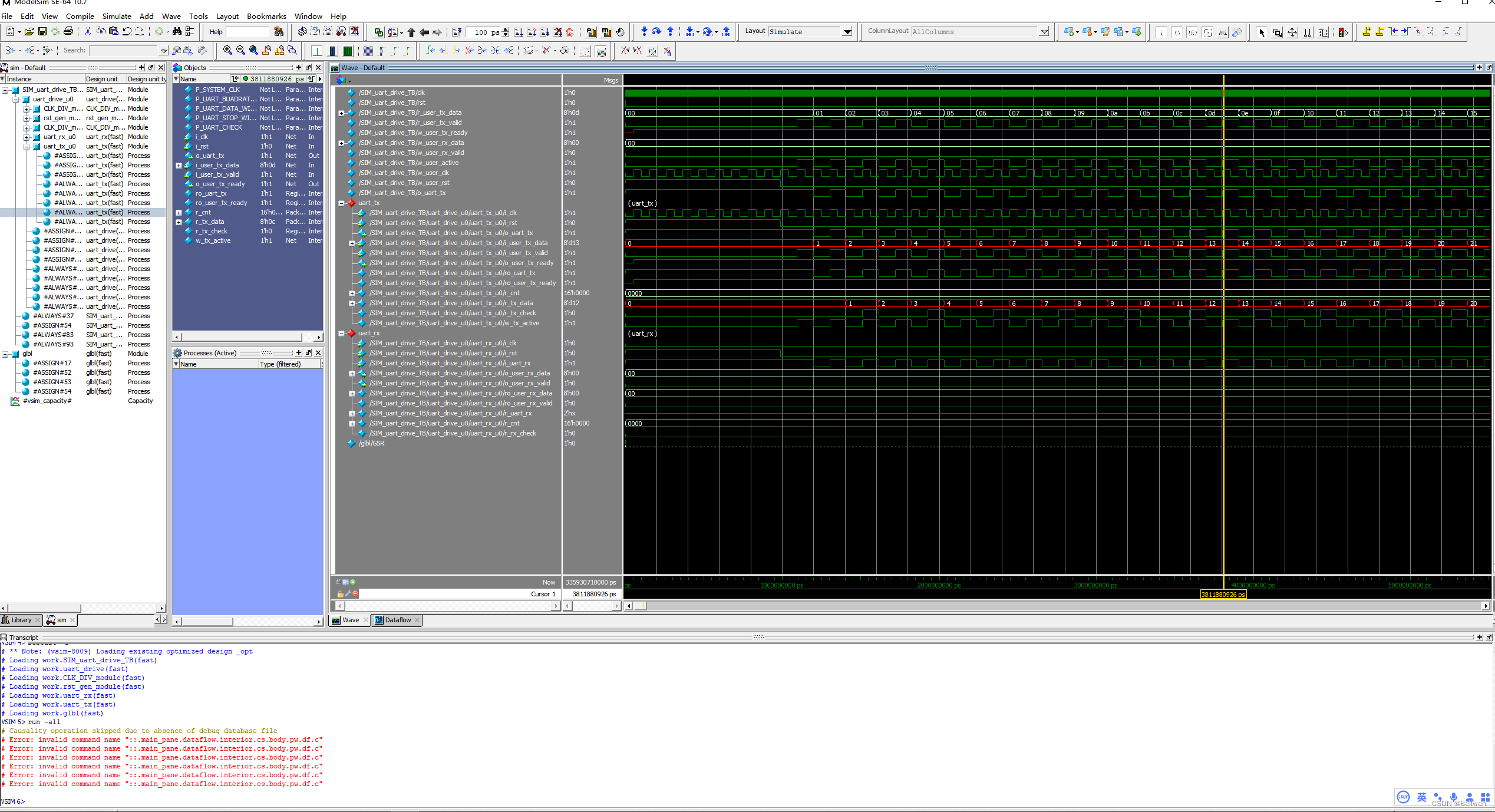

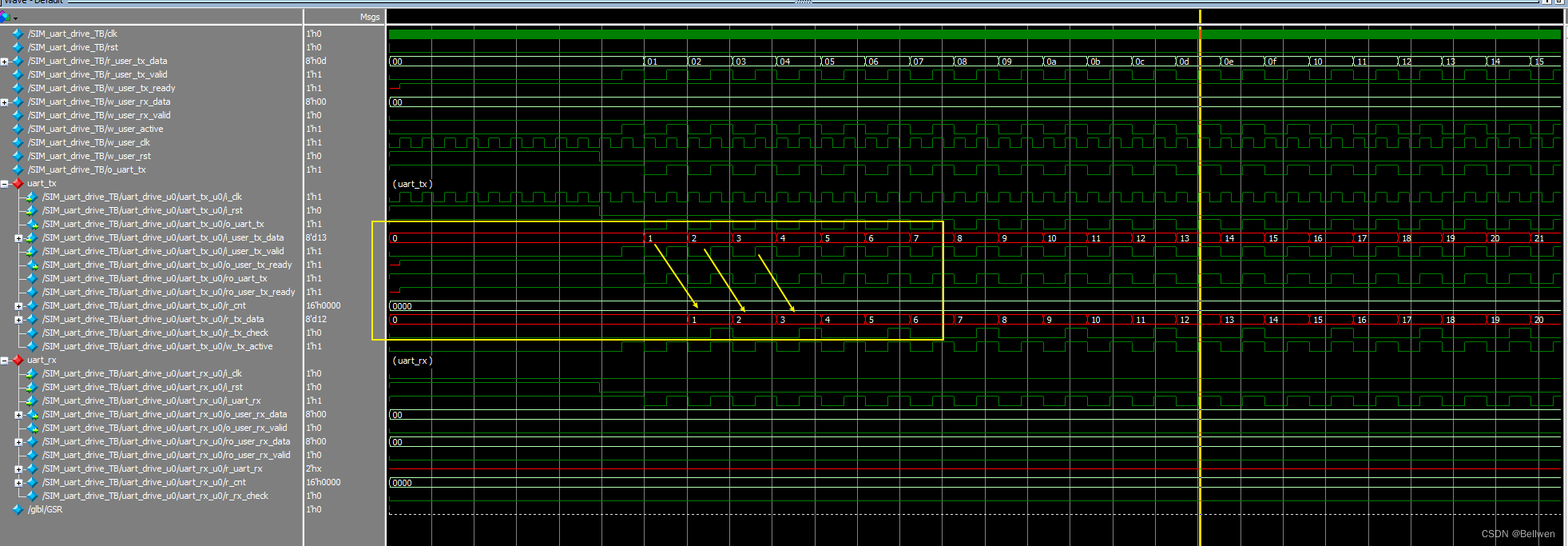

vivado联合modelsim进行仿真。

一、SIM_uart_drive_TB仿真代码

`timescale 1ns / 1ns //时间单位/时间精度

//

// Company:

// Engineer:

//

// Create Date: 2023/09/12 14:52:47

// Design Name:

// Module Name: SIM_uart_drive_TB

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module SIM_uart_drive_TB();

/****仿真语法、产生时钟与复位****/

localparam CLK_PERIOD = 20 ;

reg clk,rst;

initial begin //过程语句,只在仿真里可以使用,不可综合

rst = 1; //上电开始复位

#100; //延时100ns

@(posedge clk) rst = 0; //上电复位释放

end

always begin//过程语句,只在仿真里可以使用,不可综合

clk = 0;

#(CLK_PERIOD/2);

clk = 1;

#(CLK_PERIOD/2);

end

localparam P_USER_DATA_WIDTH = 8;

reg [P_USER_DATA_WIDTH - 1 : 0] r_user_tx_data ;

reg r_user_tx_valid ;

wire w_user_tx_ready ;

wire [P_USER_DATA_WIDTH - 1 : 0] w_user_rx_data ;

wire w_user_rx_valid ;

wire w_user_active ;

wire w_user_clk ;

wire w_user_rst ;

assign w_user_active = r_user_tx_valid & w_user_tx_ready;

uart_drive#(

.P_SYSTEM_CLK (50_000_000 ), //输入时钟频率

.P_UART_BUADRATE (9600 ), //波特率

.P_UART_DATA_WIDTH (P_USER_DATA_WIDTH ), //数据宽度

.P_UART_STOP_WIDTH (1 ), //1或者2

.P_UART_CHECK (2 ) //None=0 Odd-1 Even-2

)

uart_drive_u0

(

.i_clk (clk),

.i_rst (rst),

.i_uart_rx (o_uart_tx ),

.o_uart_tx (o_uart_tx ),

.i_user_tx_data (r_user_tx_data ),

.i_user_tx_valid (r_user_tx_valid ),

.o_user_tx_ready (w_user_tx_ready ),

.o_user_rx_data (w_user_rx_data ),

.o_user_rx_valid (w_user_rx_valid ),

.o_user_clk (w_user_clk ) ,

.o_user_rst (w_user_rst )

);

/****激励信号****/

always@(posedge w_user_clk,posedge w_user_rst)

begin

if(w_user_rst)

r_user_tx_data <= 'd0;

else if(w_user_active)

r_user_tx_data <= r_user_tx_data + 1;

else

r_user_tx_data <= r_user_tx_data;

end

always@(posedge w_user_clk,posedge w_user_rst)

begin

if(w_user_rst)

r_user_tx_valid <= 'd0;

else if(w_user_active)

r_user_tx_valid <= 'd0;

else if(w_user_tx_ready)

r_user_tx_valid <= 'd1;

else

r_user_tx_valid <= r_user_tx_valid;

end

endmodule

二、仿真结果

总结

还得练,要熟练使用modelsim进行仿真,因为比vivado快。

要会写仿真代码文件,继续多练。

结合协议时序实现UART收发器也算完结了。

评论(0)

您还未登录,请登录后发表或查看评论